## (12) United States Patent Birkett et al.

### (10) Patent No.: US 6,977,976 B1

#### (45) Date of Patent: Dec. 20, 2005

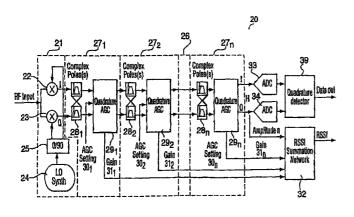

## (54) COMPLEX FILTERING/AGC RADIO RECEIVER ARCHITECTURE FOR LOW-IF **OR ZERO-IF**

# (75) Inventors: Neil Birkett, Richmond (CA); James Cherry, Ottawa (CA); William Martin

Snelgrove, Toronto (CA); Florinel Balteanu, Ottawa (CA)

Assignee: Skyworks Solutions, Inc., Irvine, CA

(\*) Notice: Subject to any disclaimer, the term of this

patent is extended or adjusted under 35

U.S.C. 154(b) by 851 days.

Appl. No.: 09/675,513

Sep. 29, 2000 (22)Filed:

#### (30)Foreign Application Priority Data

| Nov. 15, 1999 | (CA) |            |

|---------------|------|------------|

| (1) Int Cl 7  |      | H041 27/08 |

(52)455/245.2; 455/296

375/346, 349, 350, 285; 455/232.1, 234.1, 455/245.1, 245.2, 251.1, 283, 296, 278.1, 455/250.1, 226.1, 226.2, 63.1, 67.11, 67.13

References Cited (56)

## U.S. PATENT DOCUMENTS

| 4,543,546 A * | 9/1985  | Hariharan 333/173      |

|---------------|---------|------------------------|

| 5,086,437 A * | 2/1992  | Tomita 375/345         |

| 5,896,562 A * | 4/1999  | Heinonen 455/76        |

| 6,009,317 A * | 12/1999 | Wynn 455/296           |

| 6,233,227 B1* | 5/2001  | Izumi 370/280          |

| 6,324,387 B1* | 11/2001 | Kamgar et al 455/234.1 |

## OTHER PUBLICATIONS

IEEE Journal of Solid State Circuits, vol. 30, No. 12, Dec., 1995, pp. 1399-1410, Direct-Conversion Radio Transceivers for Digital Communications—ABIDI, Asad A.

IEEE Transactions on Circuits and Systems—II: Analog and Digital Signal Processing, vol. 45, No. 3, Mar., 1998, pp 269-282 Low-IF Topologies for High-Performance Analog Front Ends of Fully Integrated Receivers CROLS, Jan & Steyaert, Michiel S.J.

\* cited by examiner

Primary Examiner—Jean B. Corrielus (74) Attorney, Agent, or Firm—Gardner Groff, P.C.

### **ABSTRACT**

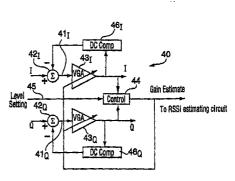

A low power IF strip architecture suitable for Zero-IF (ZIF) or low-IF (LIF) radio receivers for filtering and amplifying a received signal. The apparatus includes a plurality of sequentially connected complex filter/amplifier stages. Each stage includes a complex filter having one or more poles and an automatic gain controlled amplifier (AGC). Each AGC may be feedback or feedforward with fixed minimum and maximum gains. Each stage further includes a control circuit that produces a gain control signal for controlling the amplifier gain within the fixed minimum and maximum gains as a function of a projected amplitude level. The received signal passes through multiple stages of filtering and controlled amplification to attenuate the interfering signal and amplify the desired signal. This is done at a restricted level in each stage such that the circuits in the stages operate at efficient power saving levels. The individual gain control signals from each stage are summed in a received signal strength indicator to provide the overall gain of the apparatus. The overall gain when taken with the amplitude of the apparatus output signal determines the original strength of the desired received signal.

## 27 Claims, 7 Drawing Sheets